**SVP-723**

Модуль цифровой обработки данных на базе 2-х основных FPGA Xilinx Virtex-7 с поддержкой 2-х FMC форм-фактора VPX 6U

# Основные особенности

- Две высокопроизводительные FPGA Xilinx Virtex-7 в корпусе FFG1761 с поддержкой установки кристаллов XC7VX330T и XC7VX485T

- По два независимых 16-ти разрядных банка памяти DDR3-800 общим объёмом до 1 Гбайт на каждой FPGA

- Установка двух субмодулей FMC в соответствии со стандартом ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard с поддержкой HPC интерфейса, включая 8 дуплексных линий MGT

- Модуль форм-фактора VPX 6U, соответствующий стандартам: ANSI/VITA 46.0-2013 (воздушное охлаждение), ANSI/VITA 46.3-2012, ANSI/VITA 46.4-2012, ANSI/VITA 46.6-2013, ANSI/VITA 57.1-2010 и ANSI/VITA 65-2010 (R2012)

- Поддержка системных интерфейсов: PCI Express, Serial RapidIO, Gigabit Ethernet, XAUI (отдельно приобретаемые IP-ядра)

- Исполнение с воздушным охлаждением

# Обзор модуля

#### Особенности

Модуль SVP-723 форм-фактора VPX 6U разработан на базе высокопроизводительной серии FPGA Xilinx Virtex-7 и сочетает в себе широкие интерфейсные возможности и большой объём встроенной скоростной памяти. Поддержка установки двух субмодулей FMC стандарта ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard позволяет гибко организовать ввод/вывод необходимых пользователю сигналов, включая аналоговые (с использованием субмодулей АЦП/ЦАП), оптические и цифровые.

Модуль SVP-723 предназначен для приложений, требующих предельно высокую производительность цифровой обработки данных в реальном времени: фильтрации, спектральных преобразований, корреляционной обработки, кодирования/декодирования, работы с пакетами и т. д. Так, пиковая производительность обработки операций на целочисленных операциях умножить-аккумулировать достигает 2000 млрд./с (операнды 25 × 18 бит, аккумулятор 48 бит) для каждой FPGA, а производительность обмена FPGA с памятью DDR3 превышает 3 Гбайт/с.

### Производительность

Пропускная способность системных интерфейсов модуля (FP 1–4) превышает 128 Гбит/с (16 MGT 8 Гбит/с на двух FPGA), поддерживается широкий ряд стандартов: PCI Express вплоть до версии 3.0 (только для VX330T), Serial RapidIO, XAUI, Gigabit Ethernet, которые, в зависимости от типа коммутаторов и объединительных плат, могут сочетаться между собой в различных комбинациях (реализация интерфейсов осуществляется с помощью IP-ядер, приобретаемых отдельно).

Модуль поддерживает кольцевое соединение в составе крейта через линии EP[1:0] и EP[9:8] разъёма VPX P2 со скоростью до 25 Гбит/с.

Дуплексная пропускная способность межкристального обмена FPGA модуля превышает 50 Гбит/с (8 MGT Virtex-7 по 6,25 Гбит/с).

Пропускная способность интерфейса каждой FPGA модуля с субмодулем FMC достигает 80 Гбит/с через шины LVDS и 50 Гбит/с на приём/передачу через каналы MGT Virtex-7 (8 полнодуплексных линий по 6,25 Гбит/с). Обеспечена поддержка широкой номенклатуры стандартизованных субмодулей FMC производства ЗАО «Скан Инжиниринг Телеком» и сторонних производителей.

#### Области применения

Поддержка модулем ряда системных функций OpenVPX: тактирование и синхронизация через объединительную плату, географическая адресация и т. д., значительно облегчает интеграцию модуля во вновь создаваемые и существующие системы VPX для телекоммуникационных, промышленных и военных применений.

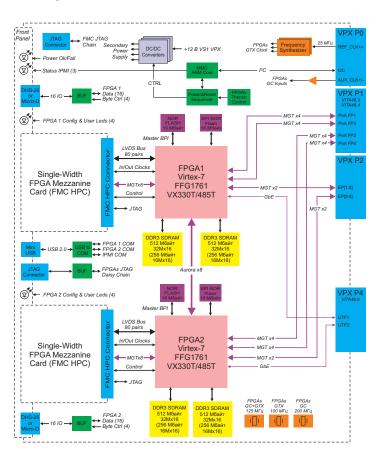

# Функциональная блок-схема

# Технические характеристики

#### Программируемая логика

Ocoбенности FPGA Xilinx Virtex-7 в корпусе FFG1761 XC7VX330T и XC7VX485T:

- свыше 75 тыс. ячеек Virtex-7 Slice;

- до 2800 блоков Virtex-7 DSP48E;

- до 1000 блоков RAM Xilinx BlockRAM по 36 кбит;

- до 14 блоков тактирования СМТ Xilinx.

До 2-х ядер PCI Express 1.0, 2.0, 3.0 x1/x2/x4/x8 — XC7VX330T

До 4-х ядер PCI Express 1.0, 2.0, 3.0 x1/x2/x4/x8 — XC7VX485T

Межкристальный обмен FPGA — 8 дуплексных линий MGT по 6,25 Гбит/с

#### Память

По два 16-ти разрядных банка памяти SDRAM DDR3-800 суммарным объёмом до 1 Гбайт на каждой FPGA

Память SPI NOR Flash 16 Мбайт на каждой FPGA

Конфигурационная память Platform Flash XL объёмом 16 Мбайт на каждой FPGA со скоростью загрузки данных в FPGA до 640 Мбит/с и доступом через интерфейс JTAG

### Разъёмы VPX

### Разъём Р0:

- сигналы тактирования REF\_CLK;

- сигналы тактирования AUX\_CLK;

- сигналы I<sup>2</sup>C.

#### Разъём Р1:

- порты FatPipe1—4 могут быть сконфигурированы одним из следующих вариантов:

- четыре канала PCI Express 1.0, 2.0, 3.0 х4 (аппаратные ядра PCI Express Xilinx + MGT Xilinx, 3.0 только для XC7VX330T);

- Serial RapidIO x4 до 3,125 Гбит/с (MGT Xilinx + программное IP-ядро Xilinx, приобретается отдельно).

## Разъём Р2:

• MGT x2 с каждой FPGA на линиях EPxx кольца backplane (поддерживается не на всех backplane).

#### Разъём Р4:

Два канала Gigabit Ethernet через порты Ultra-TP1, 2 (IP-ядро Gigabit Ethernet приобретается отдельно).

#### Соответствие стандартам

ANSI/VITA 46.0-2013 VPX Base Standard

ANSI/VITA 46.3-2012 Serial RapidIO on VPX

Fabric Connector

ANSI/VITA 46.4-2012 PCI Express on the VPX Fabric Connector

ANSI/VITA 46.6-2013 Gigabit Ethernet Control Plane on VPX

ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard

ANSI/VITA 65-2010 (R2012) OpenVPX System Standard

#### Тактирование

Набор синтезаторов сетки произвольных частот MGT FPGA

Опорные кварцевые генераторы 100 МГц (интерфейсы FPx, EP VPX) и 125 МГц (Gigabit Ethernet) для MGT FPGA, 125/200 МГц для глобального тактирования FPGA

Схема PLL очистки и умножения опорного тактового сигнала VPX REF\_CLK 25 МГц до 250 МГц (для MGT основных FPGA)

#### Разъём FMC

Поддержка установки двух субмодулей FMC одиночной ширины (Single Width) в конструктиве с воздушным охлаждением с задействованием областей 1–3

Стыковочная высота FMC 10 мм

Интерфейс каждого субмодуля FMC HPC:

- 80 пар LVDS, пропускная способность до 80 Гбит/с;

- подключение сигналов \*\_СС ко входам СС FPGA;

- поддержка четырех линий глобального тактирования LVDS;

- 8 дуплексных мультигигабитных пар DP0–DP7 с двусторонней пропускной способностью до 50 Гбит/с;

- две линии тактирования MGT FPGA с разъёма FMC.

Поддержка JTAG 3,3 В с автоматической коммутацией канала

Поддержка сигналов  $I^2C$  (IPMI FMC), PRSNT, PowerGood

Соответствие стандарту ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard по требованиям к питающим напряжениям и токам нагрузки субмодулей

Уровень напряжения по линиям VADJ/VIO\_B\_M2C +1,8 В

#### Внешние и отладочные интерфейсы

Отладочные COM-порты для каждой FPGA с единым интерфейсом USB 2.0 на передней панели

Буферизованный JTAG IEEE 1149.1 FPGA на передней панели

Внутренний буферизованный порт JTAG IEEE 1149.1 для FMC

Два буферизованных 16-ти разрядных цифровых порта передней панели с побайтным управлением

### Системные функции

Поддержка шины  $I^2C$  VPX (линии SM0, SM1) IPMI

Поддержка географической адресации (GA0–GA4)

Обработка сигнала системного сброса VPX SYSRESET#

Обработка сигнала маскируемого сброса MaskableReset

Встроенный контроль напряжений и тока потребления

Встроенный температурный контроль

#### Энергопотребление

Потребляемая мощность модуля цифровой обработки данных: от 120 до 150 Вт

Распределение потребляемой мощности по линии питания:

- +12 В (VS1): до 10 А (120 Вт) (полная нагрузка, без учета FMC;

- +12 B (VS1): до 10,8 A (150 Вт) (полная нагрузка, с двумя FMC).

#### Условия эксплуатации

Охлаждение: воздушное

Диапазон рабочих температур: коммерческий (0...+50 °C) или индустриальный (-40...+85 °C)

Температура хранения: -40...+85 °C

Влажность: 10-95 % без конденсата

Возможность нанесения влагозащитного покрытия для жёстких условий

### Размеры

Форм-фактор: VPX 6U в слот 1" Размеры:  $160 \times 233 \times 25,06$  мм

# Информация для заказа

Модуль с поддержкой двух субмодулей FMC HPC, двумя буферизованными 16-ти разрядными портами на внутренних разъёмах ЕНF с защелками, панелью VPX 1″. Программное обеспечение поддержки модуля, а также отладочные кабели в комплект поставки не входят, их приобретение оговаривается отдельно.

Возможна поставка модуля в другом температурном диапазоне по согласованию.

Основная FPGA Xilinx

Обе предустановленные на плату FPGA одинаковые и семейста Virtex-7

**FM330T1**: XC7VX330T-1 **FM330T2**: XC7VX330T-2

FM485T1: XC7VX485T-1

FM485T2: XC7VX485T-2

Ш

Объём установленной памяти FPGA

RFM2x32Mx16: 1 Гбайт в двух 16-ти разрядных банках для каждой

FPGA XC7VLX330T, XC7VLX485T

**RFM2x16Mx16:** 512 Мбайт в двух 16-ти разрядных банках для

каждой FPGA XC7VLX330T, XC7VLX485T

III Передняя панель

**FP2:** Установлена стандартная передняя панель FMC

**FPN:** Заказная передняя панель, тип устанавливаемого субмодуля

оговаривается при заказе дополнительно

IV Вывод буферизованных цифровых портов

В0: Вывод цифровых портов на переднюю панель не производится

**BIO2**: Установлен буфер и разъём цифрового порта (LPC, HPC)

**BDHS0:** Разъёмы DHS (DHS-26M), 26 выводов, винт

**ВМD:** Разъемы Micro-D (Molex 83614-9016), 25 выводов, винт

V Исполнение (температурный диапазон)

**Т0:** Коммерческое (0...+50 °C) **Т1:** Индустриальное (-40...+85 °C)

VI

CV0: Без влагозащитного покрытия

**CV1:** С влагозащитным покрытием

VII

**CL1:** Кондуктивное **CL0:** Воздушное

Пример кода изделия: SVP-723-FM330T1-RFM2x32Mx16-FP2-BDHS0-T1-CV1-CL1

SVP-723 — Модуль цифровой обработки данных на базе 2-х основных FPGA Xilinx Virtex-7 с поддержкой 2-х FMC форм-фактора VPX 6U Основная FPGA Xilinx: XC7VX330T-1

Объём установленной памяти FPGA: 1 Гбайт в двух 16-ти разрядных банках для каждой FPGA XC7VLX330T, XC7VLX485T

Передняя панель: Установлена стандартная передняя панель FMC

Вывод буферизованных цифровых портов: Разъёмы DHS (DHS-26M), 26 выводов, винт

Исполнение (температурный диапазон): Индустриальное (−40...+85 °C)

Покрытие: С влагозащитным покрытием

Охлаждение: Кондуктивное

Возможны другие конфигурации модуля по индивидуальному запросу. За дополнительной информацией обращайтесь в SET.

# Контактная информация

ЗАО «Скан Инжиниринг Телеком» Россия, 394030, г. Воронеж, ул. Свободы, 75 Тел.: +7 (473) 272-71-01, факс.: +7 (473) 251-21-99 www.setdsp.ru

Электронная почта:

Отдел продаж: sales@setdsp.ru

ООО «Скан Инжиниринг Телеком - СПб» Россия, 199106, г. Санкт-Петербург, 22-я линия В.О., д. 3, корп. 1, лит. М. Тел.: +7 (812) 406-99-95, +7 (812) 406-99-96 www.setdsp.ru

Электронная почта:

Отдел продаж: sales.spb@setdsp.ru

3AO «Скан Инжиниринг Телеком». Все права защищены. © 1991–2018 Документ DS-SVP-723 1.1 создан в ООО «Скан Инжиниринг Телеком - СПб». Все права защищены. © 2018