**SVP-726**

Модуль цифровой обработки данных на базе 2-х основных FPGA Xilinx Virtex-7 с поддержкой 2-х FMC форм-фактора VPX 6U

### Основные особенности

- Две высокопроизводительные FPGA Xilinx Virtex-7 с поддержкой установки кристаллов вплоть до XC7VX1140T (до 1,1 млн. логических ячеек каждый) и суммарной пиковой производительностью свыше 5 ТМАС/с

- Четыре независимых 16-ти разрядных банка памяти DDR3-800 общим объёмом до 2 Гбайта на каждой FPGA

- Установка двух субмодулей FMC в соответствии со стандартом ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard с поддержкой HPC интерфейса, включая 8 дуплексных линий MGT

- Модуль форм-фактора VPX 6U, соответствующий стандартам: ANSI/VITA 46.0-2013 (воздушное охлаждение), ANSI/VITA 46.3-2012, ANSI/VITA 46.4-2012, ANSI/VITA 46.6-2013, ANSI/VITA 57.1-2010 и ANSI/VITA 65-2010 (R2012)

- Поддержка системных интерфейсов: PCI Express 1.0, 2.0, 3.0, Gigabit Ethernet, Serial RapidIO, XAUI (отдельно приобретаемые IP-ядра)

- Исполнение с воздушным охлаждением

# Обзор модуля

#### Особенности

Модуль SVP-726 разработан на базе высокопроизводительной серии FPGA Xilinx Virtex-7 и сочетает в себе широкие интерфейсные возможности и большой объём встроенной скоростной памяти. Реализованная поддержка установки двух субмодулей FMC HPC стандарта ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard позволяет гибко организовать ввод/вывод необходимых пользователю сигналов, включая аналоговые (с использованием субмодулей АЦП/ЦАП), оптические и цифровые.

Модуль SVP-726 предназначен для приложений, требующих предельно высокую производительность цифровой обработки данных в реальном времени: фильтрации, спектральных преобразований, корреляционной обработки, кодирования/декодирования, работы с пакетами и т. д. Так, пиковая производительность обработки операций в секунду над операндами с фиксированной запятой достигает 2600 млрд./с (VSX690T, операнды 25 × 18 бит, аккумулятор 48 бит) для каждой FPGA, а суммарная производительность обмена с памятью DDR3 составляет свыше 6 Гбайт/с (четыре 16-ти разрядных банка по 512 Мбайт).

#### Производительность

Пропускная способность системных интерфейсов модуля (Fat Pipe 1–4) превышает 128 Гбит/с, поддерживается широкий ряд стандартов: PCI Express вплоть до версии 3.0, Serial RapidIO, XAUI, Gigabit Ethernet, которые, в зависимости от типа коммутаторов и объединительных плат, могут сочетаться между собой в различных комбинациях (реализация интерфейсов осуществляется с помощью IP-ядер, приобретаемых отдельно).

Основные FPGA посредством 8-ми линий MGT имеют выход на разъёмы тылового ввода/вывода (разъёмы VPX P3 и P5) со скоростью двунаправленного обмена до 50 Гбит/с, что позволяет расширять возможности модуля за счет подключения разнообразных периферийных плат, например, с оптическими приёмопередатчиками, процессорами DSP с Serial RapidIO и т. д.).

Пропускная способность интерфейса модуля с субмодулем FMC достигает 80 Гбит/с через шины LVDS и 52 Гбит/с на приём/передачу через каналы GTX (8 полнодуплексных линий по 6,25 Гбит/с). Ввиду стандартизованного интерфейса FMC обеспечивается поддержка широкого ряда субмодулей FMC как производства 3AO «Скан Инжиниринг Телеком», так и сторонних производителей.

Дуплексная пропускная способность межкристального обмена FPGA модуля превышает 50 Гбит/с (8 MGT Virtex-7 по 6,25 Гбит/с). Модуль поддерживает кольцевое соединение в составе крейта через линии EP[7:0], EP[15:8] разъёмы VPX P2 до 100 Гбит/с.

### Области применения

Поддержка модулем ряда системных функций OpenVPX: тактирование и синхронизация через объединительную плату, географическая адресация и т. д., значительно облегчает интеграцию модуля во вновь создаваемые и существующие системы VPX для телекоммуникационных, промышленных

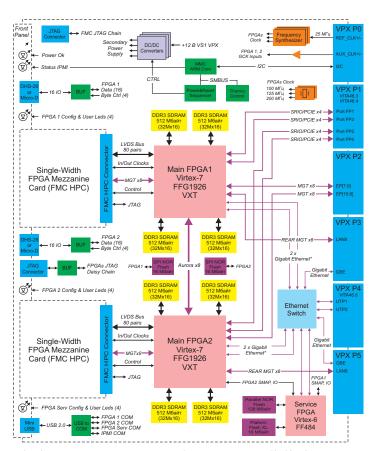

# Функциональная блок-схема

\* - Virtex-7 - программная реализация на базе логического ядра Gigabit Ethernet (TEMAC), приобретается отдельно

# Технические характеристики

#### Программируемая логика

FPGA Xilinx Virtex-7 из ряда:

- XC7VX690T/980T/1140T;

- особенности FPGA:

- свыше 178 тыс. ячеек Virtex-7 Slice (XC7VX1140T);

- до 3600 блоков Virtex-7 DSP48E (XC7VX980T);

- до 1880 блоков RAM Xilinx BlockRAM по 36 кбит;

- до 24 блоков тактирования ММСМ;

- до 4-х аппаратных ядер PCI Express 1.0, 2.0 x1/x4/x8.

Сервисная FPGA Xilinx Virtex-6 XC6VLX75T:

- 11640 ячеек Virtex-6 Slice;

- 156 блоков RAM Xilinx BlockRAM по 36 кбит;

- четыре аппаратных блока Ethernet MAC 1000 Мбит/с.

#### Память

Четыре независимых 16-ти разрядных банка памяти DDR3-800 объёмом по 512 Мбайт на основных FPGA

Память SPI NOR Flash 16 Мбайт на каждой FPGA (кроме сервисной)

Память NOR Flash 128 Мбайт для хранения конфигурационных файлов основных FPGA

Память Platform Flash XL объёмом 16 Мбайт на сервисной FPGA для хранения конфигурационных файлов и доступом через JTAG со скоростью 640 Мбит/с

#### Тактирование

Набор синтезаторов сетки произвольных частот MGT FPGA

Опорные кварцевые генераторы 100 МГц (интерфейсы FPx, EP VPX) и 125 МГц (Gigabit Ethernet) для MGT FPGA, 125/200 МГц для глобального тактирования FPGA

Схема PLL очистки и умножения опорного тактового сигнала VPX REF\_CLK 25 МГц до 250 МГц (для MGT основных FPGA)

### Внешние и отладочные интерфейсы

Отладочные COM-порты для каждой FPGA с единым интерфейсом USB 2.0 на передней панели

Буферизованный JTAG IEEE 1149.1 FPGA на передней панели

Внутренний буферизованный порт JTAG IEEE 1149.1 для FMC

Два буферизованных 16-ти разрядных цифровых порта передней панели с побайтным управлением

#### Разъёмы VPX

#### Разъём Р0:

- сигналы тактирования REF\_CLK;

- сигналы тактирования AUX\_CLK;

- сигналы I<sup>2</sup>C.

#### Разъём Р1:

- порты FatPipe1–4 могут быть сконфигурированы одним из следующих вариантов:

- четыре канала PCI Express 1.0, 2.0, 3.0 х4 (аппаратные ядра PCI Express Xilinx + MGT Xilinx);

- Serial RapidIO x4 до 3,125 Гбит/с (MGT Xilinx + программное IP-ядро Xilinx).

#### Разъём Р2:

два канала MGT x8 с каждой FPGA на линиях EPxx кольца backplane (поддерживается не на всех backplane).

#### Разъём Р3:

- REAR MGT x8 Канал Gigabit Ethernet на линии LAN8:

- Канал Gigabit Ethernet через порты GBE.

#### Разъём Р4

• Два канала Gigabit Ethernet через порты Ultra-TP1, 2 (IP-ядро Gigabit Ethernet приобретается отдельно).

#### Разъём Р5:

- REAR MGT x8 Канал Gigabit Ethernet на линии LAN8;

- Канал Gigabit Ethernet через порты GBE.

### Соответствие стандартам

**Fabric Connector**

ANSI/VITA 46.0-2013 VPX Base Standard

ANSI/VITA 46.3-2012 Serial RapidIO on VPX

ANSI/VITA 46.4-2012 PCI Express on the VPX Fabric Connector

ANSI/VITA 46.6-2013 Gigabit Ethernet Control Plane on VPX

ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard

ANSI/VITA 65-2010 (R2012) OpenVPX System Standard

### Системные функции

Поддержка шины  $I^2C$  VPX (линии SM0, SM1) интеллектуальной системы управления IPMI

Поддержка географической адресации (GA0–GA4)

Обработка сигнала системного сброса VPX SYSRESET#

Обработка сигнала маскируемого сброса MaskableReset

Встроенный контроль напряжений и тока потребления

Встроенный температурный контроль

#### Разъем FMC

Поддержка установки двух субмодулей FMC одиночной ширины (Single Width) в конструктиве с воздушным охлаждением с задействованием областей 1–3

Стыковочная высота: FMC 10 мм

Интерфейс каждого субмодуля FMC HPC:

- 80 пар LVDS, пропускная способность до 80 Гбит/с;

- подключение сигналов \*\_CC ко входам CC FPGA;

- поддержка четырех линий глобального тактирования LVDS;

- 8 дуплексных мультигигабитных пар DP0–DP7 с двусторонней пропускной способностью до 50 Гбит/с;

- две линии тактирования MGT FPGA с разъёма FMC.

Поддержка JTAG 3,3 В с автоматической коммутацией канала

Поддержка сигналов  $I^2C$  (IPMI FMC), PRSNT, PowerGood

Соответствие стандарту ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard по требованиям к питающим напряжениям и токам нагрузки субмодулей

Уровень напряжения по линиям VADJ/VIO B M2C +1,8 B

#### Энергопотребление

Потребляемая мощность модуля цифровой обработки сигналов: от 140 до 170 Вт

Распределение потребляемой мощности по линии питания:

- +12 B (VS1): до 11,5 A (140 Вт) (при полной нагрузке, без учета FMC;

- +12 В (VS1): до 14,1 Å (170 Вт) (при полной нагрузке, с двумя FMC субмодулями).

### Условия эксплуатации

Охлаждение: воздушное

Диапазон рабочих температур: коммерческий (0...+50 °C) или индустриальный (-40...+85 °C)

Температура хранения: -40...+85 °C

Влажность: 10-95 % без конденсата

Возможность нанесения влагозащитного покрытия для жёстких условий

### Размеры

Форм-фактор: VPX 6U в слот 0,8″, либо 1″

Размеры: 160 × 233 × 25,06 мм

# Информация для заказа

Модуль с поддержкой двух субмодулей FMC HPC, двумя буферизованными 16-ти разрядными портами на внутренних разъёмах EHF с защелками, сервисной FPGA XC6VLX75T, с передней планкой VPX 1" с воздушным охлаждением. Программное обеспечение поддержки модуля, а также отладочные кабели в комплект поставки не входят, их приобретение оговаривается отдельно. Приобретение логических ядер (IP Core) Serial RapidIO и Gigabit Ethernet (TEMAC) оговаривается отдельно. Настоятельно рекомендуется перед заказом модуля ознакомится с его техническим описанием

Возможна поставка модуля в другом температурном диапазоне по согласованию.

Основная FPGA Xilinx

Обе предустановленные на плату FPGA одинаковые и семейста Virtex-7

FM690T1: XC7VX690T-1 FM690T2: XC7VX690T-2 FM980T1: XC7VX980T-1 FM980T2: XC7VX980T-2 FM1140T1: XC7VX1140T-1 FM1140T2: XC7VX1140T-2

Объём установленной памяти Ш **FPGA**

RFM4x16Mx16/800: 1 Гбайт в четырех 16-ти разрядных банках

**RFM4x32Mx16/800:** 2 Гбайта в четырех 16-ти разрядных банках

Передняя панель Ш

FP2: Установлена стандартная передняя панель

**FPN:** Заказная передняя панель, тип устанавливаемого субмодуля оговаривается при заказе дополнительно

Вывод буферизованных IV цифровых портов

В0: Вывод цифровых портов на переднюю панель не производится

ВІО2: Установлен буфер и разъём цифрового порта (LPC, HPC)

**BDHS0:** Разъёмы DHS (DHS-26M), 26 выводов,

**ВМD:** Разъемы Micro-D (Molex 83614-9016), 25 выводов, винт

Установка входа внешней синхронизации через разъём SSMC передней панели

Опция TR1 не доступна при выборе опции BIO2.

**TR0**: Вход внешней синхронизации отсутствует

TR1: Вход внешней синхронизации предустановлен

Исполнение (температурный V١ диапазон)

**Т0:** Коммерческое (0...+50 °C) **Т1**: Индустриальное (-40...+85 °C)

Покрытие

CV0: Без влагозащитного покрытия CV1: С влагозащитным покрытием

Охлаждение VIII

CL1: Кондуктивное **CL0:** Воздушное

Пример кода изделия: SVP-726-FM690T1-RFM4x32Mx16/800-FP2-BDHS0-TR1-T1-CV1-CL1

SVP-726 — Модуль цифровой обработки данных на базе 2-х основных FPGA Xilinx Virtex-7 с поддержкой 2-х FMC форм-фактора VPX 6U Основная FPGA Xilinx: XC7VX690T-1

Объём установленной памяти FPGA: 2 Гбайта в четырех 16-ти разрядных банках

Передняя панель: Установлена стандартная передняя панель FMC

**Вывод буферизованных цифровых портов:** Разъёмы DHS (DHS-26M), 26 выводов, винт

Установка входа внешней синхронизации через разъём SSMC передней панели: Вход внешней синхронизации предустановлен

Исполнение (температурный диапазон): Индустриальное (-40...+85 °C)

Покрытие: С влагозащитным покрытием

Охлаждение: Кондуктивное

Возможны другие конфигурации модуля по индивидуальному запросу. За дополнительной информацией обращайтесь в SET.

# Контактная информация

ЗАО «Скан Инжиниринг Телеком» Россия, 394030, г. Воронеж, ул. Свободы, 75 Тел.: +7 (473) 272-71-01, факс.: +7 (473) 251-21-99 www.setdsp.ru

Электронная почта:

Отдел продаж: sales@setdsp.ru

ООО «Скан Инжиниринг Телеком - СПб» Россия, 199106, г. Санкт-Петербург, 22-я линия В.О., д. 3, корп. 1, лит. М.

Тел.: +7 (812) 406-99-95, +7 (812) 406-99-96 www.setdsp.ru

Электронная почта:

Отдел продаж: sales.spb@setdsp.ru

ЗАО «Скан Инжиниринг Телеком». Все права защищены. © 1991–2018 Документ DS-SVP-726 1.1 создан в ООО «Скан Инжиниринг Телеком - СПб». Все права защищены. © 2018