Основные характеристики

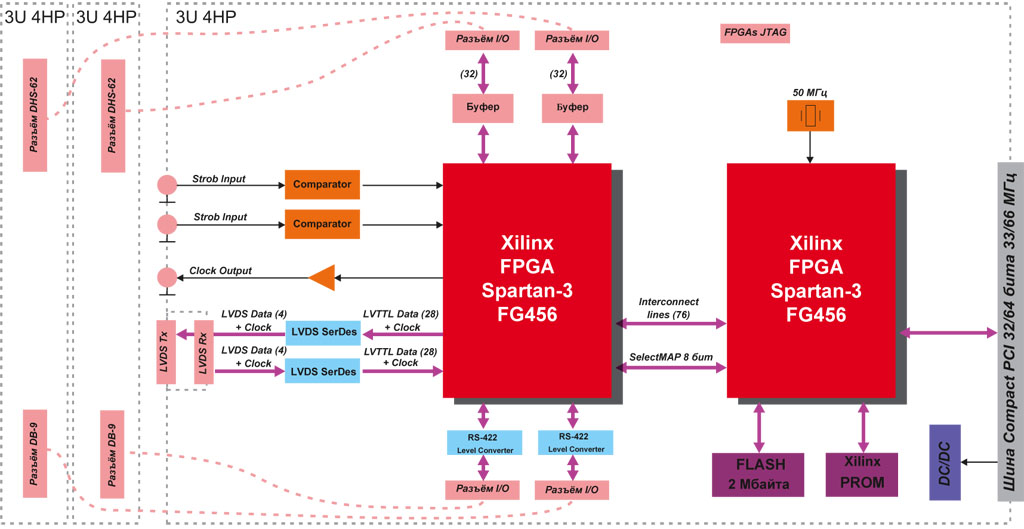

- Основная FPGA Xilinx

Spartan-3 в корпусе FG456 из ряда: XC3S400, XC3S1000, XC3S1500, XC3S2000 - Интерфейсная FPGA Xilinx

Spartan-3 в корпусе FG456 из ряда: XC3S400, XC3S1000 - Два компаратора внешнего стробирования: +1,5±0,1 В, либо +2,35±0,1 В

- Два буферизованных цифровых порта и два последовательных коммуникационных

порта

RS-422 - Канал приёма/передачи данных стандарта LVDS

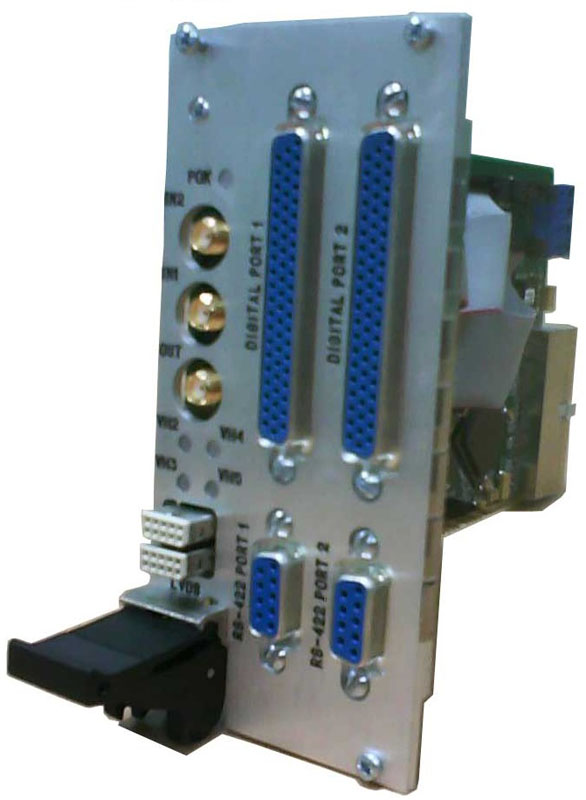

- Модуль

форм-фактора CompactPCI 3U4–12 HPPCI 32 бита/33 МГц , соответствующий стандарту PICMG 2.0 Rev 3.0

Описание

Особенности

Модуль XDSP-53 выполнен в конструктиве CompactPCI 3U с поддержкой системного

интерфейса

Особенности

Модуль XDSP-53 разработан для приложений, требующих высокую производительность,

высокую скорость передачи данных и низкую латентность. Модуль использует максимум возможностей

FPGA Xilinx

Модуль имеет дуплексный канал LVDS c производительностью не менее

Области применения

Модуль XDSP-53 форм-фактора CompactPCI 3U предназначен для решения задач

управления периферийными устройствами посредством буферизованных портов ввода/вывода

(до