Основные характеристики

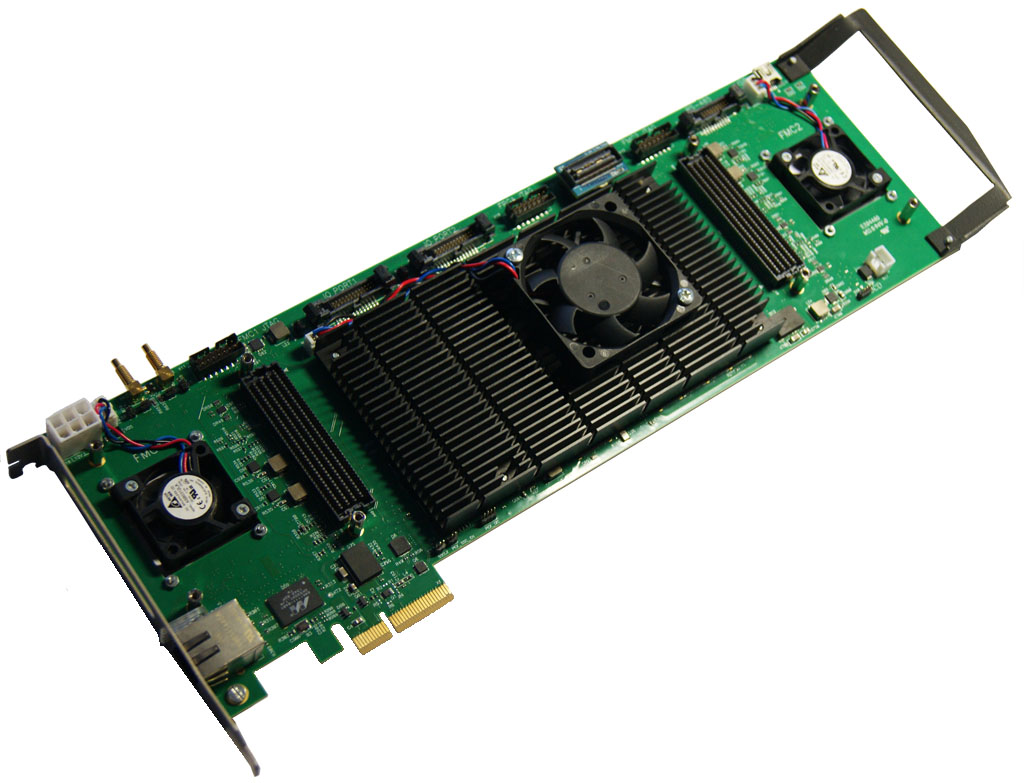

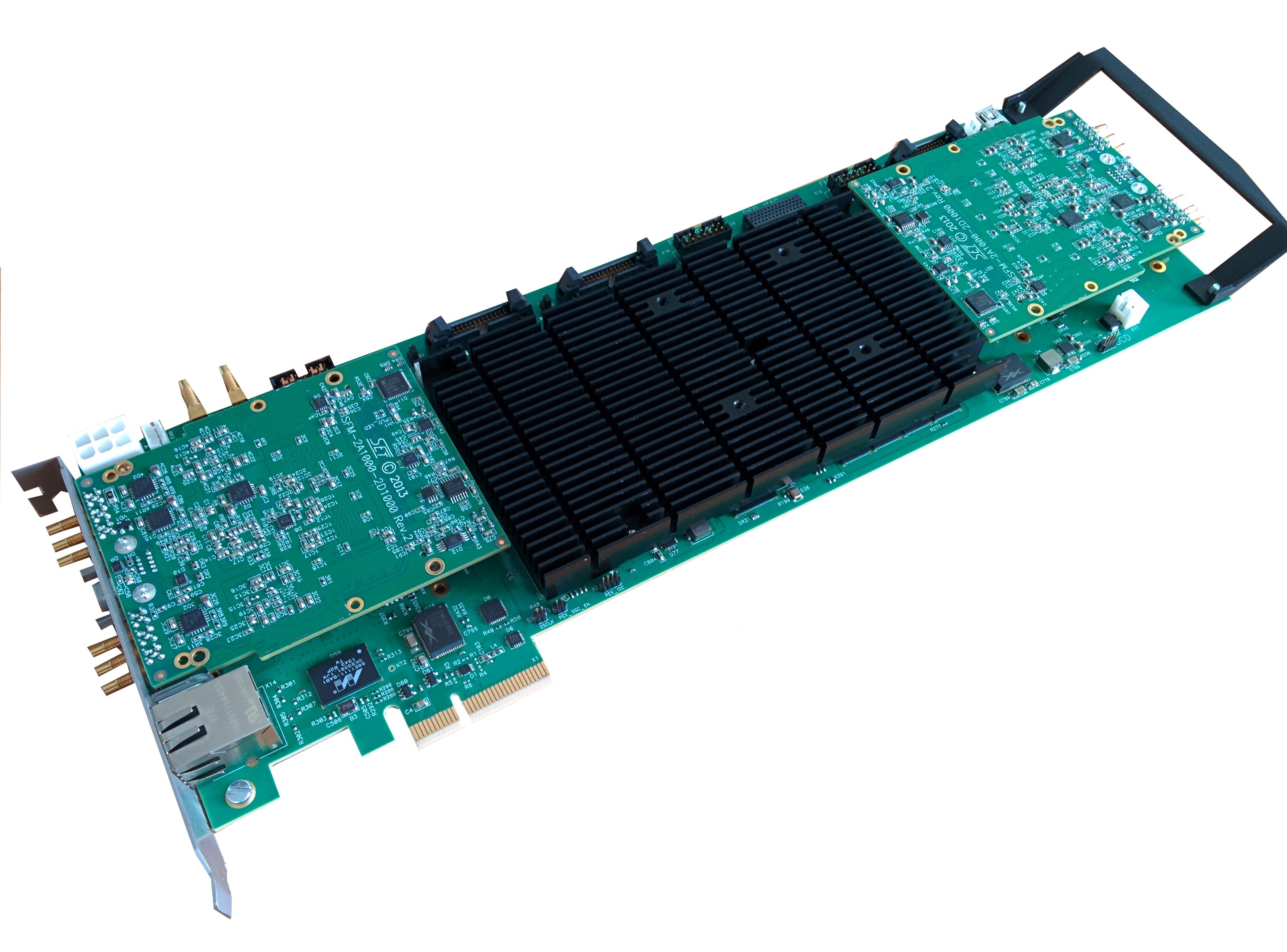

- Модуль форм-фактора PCIe стандартной высоты, полной длины, соответствующий стандарту PCIe 2.0 Base Specification

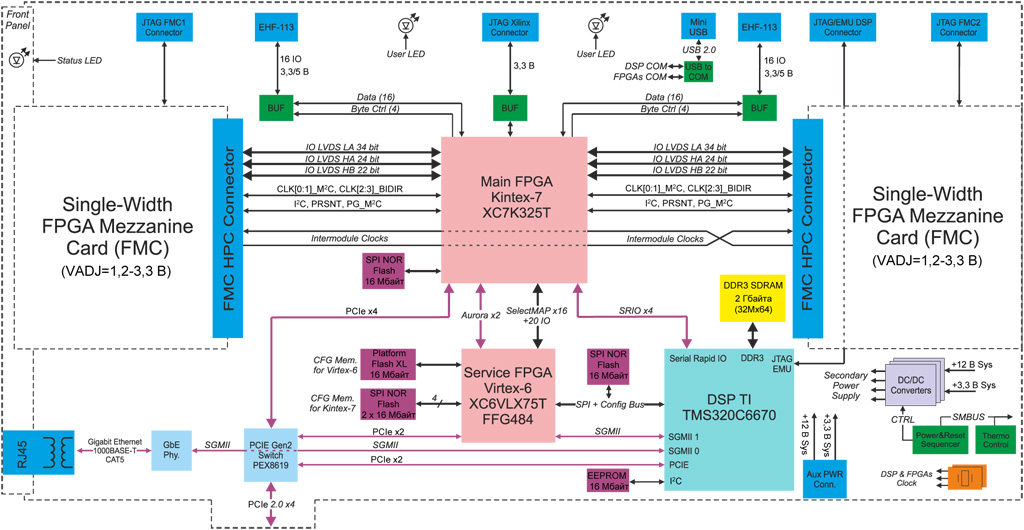

- Высокопроизводительная FPGA Xilinx

Kintex-7 XC7K325T с поддержкой установки кристалла XC7K410T с производительностью свыше2,8 TMAC/с - Высокопроизводительная система на кристалле: четырехъядерный DSP TMS320C6670 Texas Instruments (TI)

64-х разрядный банк памяти DSP DDR3 2 Гбайта- Установка двух субмодулей FMC в соответствии

со стандартом ANSI/VITA

57.1-2010 FPGA Mezzanine Card (FMC) Standard с поддержкой HPC интерфейса - Дополнительная FPGA Xilinx

Virtex-6 конфигурирования основной FPGA через PCIe и из встроенной памяти NOR Flash 32 Мбайт - Поддержка системных интерфейсов Gigabit Ethernet и PCIe 2.0 x4

Описание

Особенности

Модуль TS-PCIE, разработанный на базе высокопроизводительной FPGA Xilinx

Производительность

Пиковая производительность обработки FPGA

Наряду с высокой производительностью модуль предоставляет возможность организации

системного интерфейса с пропускной способностью

На модуле установлена служебная FPGA Xilinx

Пропускная способность интерфейса модуля с каждым субмодулем FMC достигает

Совместимость с операционными системами (ОС)

Контроллеры интерфейсов и интегрированные устройства несущий модуля цифровой обработки

сигналов не требуют написания специального программного обеспечения, все поставляемые

драйверы совместимы с большинством ОС. Стандартная поставка модуля

обеспечивает драйверную поддержку в следующих ОС: Microsoft Windows 7/8.1/10,

Embedded Standard 7/8.1, Server 2008 R2 SP1/2012/2012 R2, QNX Neutrino RTOS 6.5.0/6.6.0,

ЗОСРВ «Нейтрино» (КПДА.10964-01), Astra

Linux Special Edition 1.5, защищённая ОС «Заря», МСВС 3.0

Области применения

Модуль цифровой обработки сигналов TS-PCIE разработан для приложений, предъявляющих высокие требования к производительности в задачах, где применяется DSP.

Модуль может применяться при решении следующих задач: цифровой радиоприём, радиолокация, специальный анализ.