Основные характеристики

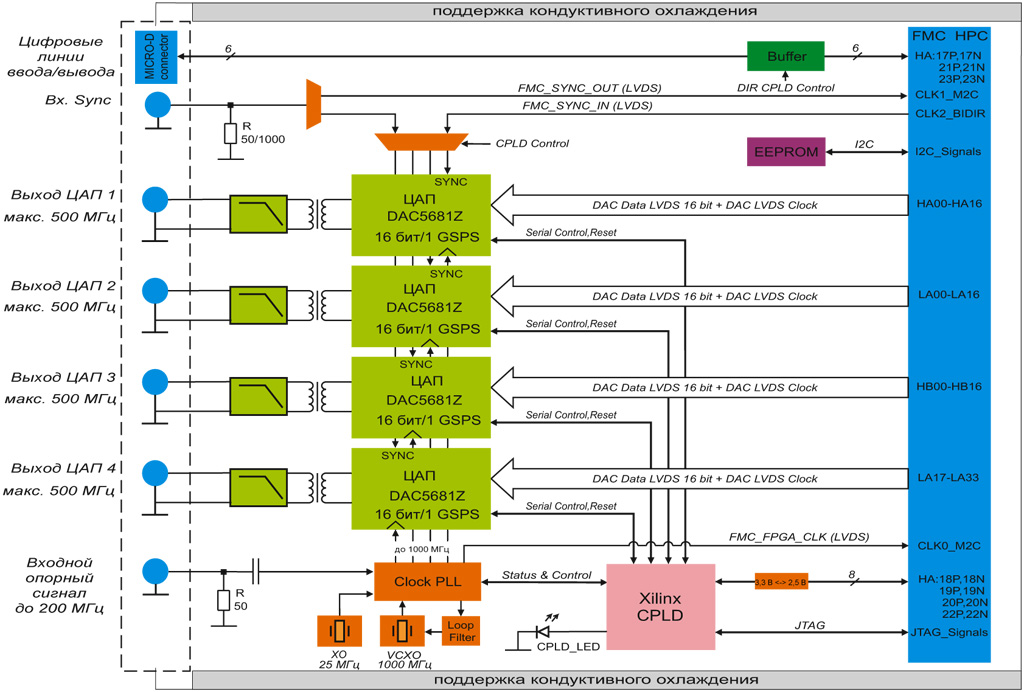

- Четыре канала интерполирующих ЦАП: 16 бит 1000 МГц

- Аналоговая полоса тракта: 500 МГц

- Широкий выбор предустанавливаемых выходных фильтров

- Входы внешней синхронизации и тактирования, синхронизация с FMC

- Встроенный высокостабильный опорный генератор

- Программное управление настройками ЦАП и схемой тактирования

Форм-фактор FMC одиночной ширины с воздушным или кондуктивным охлаждением

Описание

Особенности

Субмодуль

Субмодуль построен на базе

Высокая производительность

Высокая пропускная способность и отличные динамические характеристики делают оптимальным использование субмодуля для широкого ряда приложений, требующих генерации сигналов сложной формы: широкополосные системы связи (LTE, WCDMA, WiMAX), радиолокация, измерительная техника и т. д.

Аналоговая полоса тракта ЦАП составляет 500 МГц и может быть адаптирована под приложение Заказчика с использованием широкой линейки ФНЧ и полосовых фильтров.

Гибкая схема узла тактирования на базе ФАПЧ с малошумящим ГУН 1000 МГц, управляемая по последовательному интерфейсу SPI, позволяет работать как с источником внешнего тактирования частотой от 10 МГц до 200 МГц, так и от встроенного высокостабильного опорного генератора с номиналом частоты 25 МГц.

Области применения

Основное предназначение субмодуля: широкополосные системы связи, радиолокация, измерительная техника и т. д.