Основные характеристики

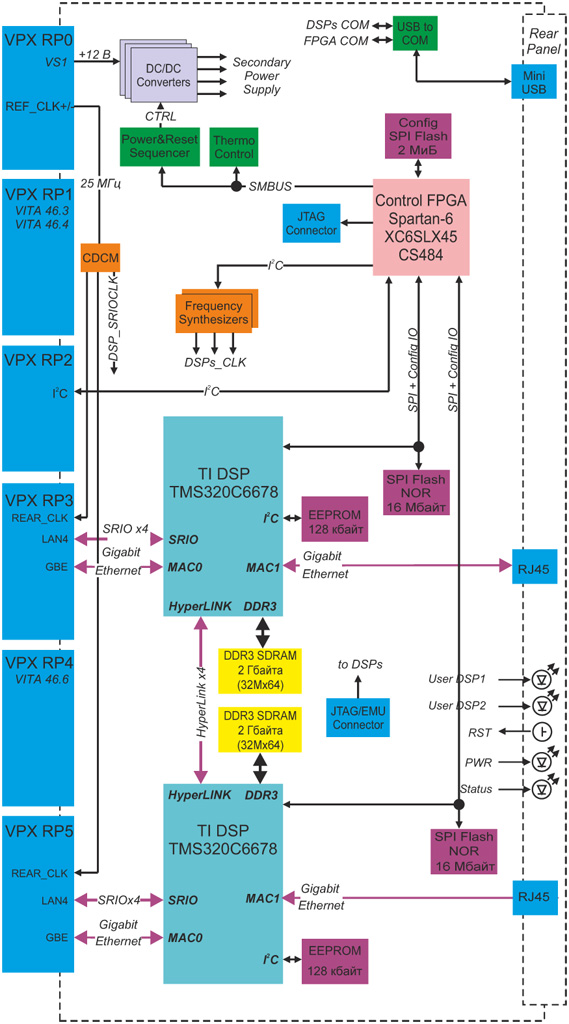

- Две высокопроизводительные системы на кристалле — два восьмиядерных цифровых сигнальных процессора (DSP) TMS320C6678 Texas Instruments (TI)

- Производительность обработки данных свыше 640 млрд. операций в секунду над операндами с фиксированной запятой или 320 млрд. операций в секунду с плавающей точкой

- По 64-х разрядному банку памяти DDR3 до 2 Гбайта для каждого процессора

- Модуль форм-фактора VPX 6U, соответствующий стандартам:

ANSI/VITA

46.0-2013 (воздушное охлаждение) и ANSI/VITA46.10-2009 (R2015) - Поддержка системных интерфейсов: Gigabit Ethernet — 2 шт., SRIO 2.1 x4 — 2 шт.

- Межкристальный интерфейс: HyperLink x4 50

Гбит/с

Описание

Особенности

Модуль SVR-420 в

Управление всем множеством аппаратных ресурсов процессоров организовано посредством архитектуры KeyStone

Multicore TI, предоставляющей высокопроизводительный неблокирующий доступ ко всем компонентам процессора,

и включающей в себя четыре основных элемента: менеджер пакетов Multicore Navigator с обработкой до 8192

запросов, широкополосную пакетную шину TeraNet с пропускной способностью до

Производительность

Тактовая частота вычислительных ядер процессоров 1,25 ГГц, суммарная пиковая производительность составляет свыше 640 млрд. операций в секунду над операндами с фиксированной запятой или 470 млрд. операций с плавающей запятой. Столь высокая производительность обработки предопределяет применение модуля для построения высокопроизводительных систем цифровой обработки сигналов в задачах фильтрации, спектральных преобразований, корреляционной обработки.

Интерфейсные возможности модуля включают два низколатентных канала SRIO x4, до

Области применения

Поддержка модулем ряда системных функций OpenVPX: тактирование и синхронизация через объединительную плату, географическая адресация и т. д., значительно облегчает интеграцию модуля во вновь создаваемые и существующие системы VPX для телекоммуникационных, промышленных и военных применений.