Основные характеристики

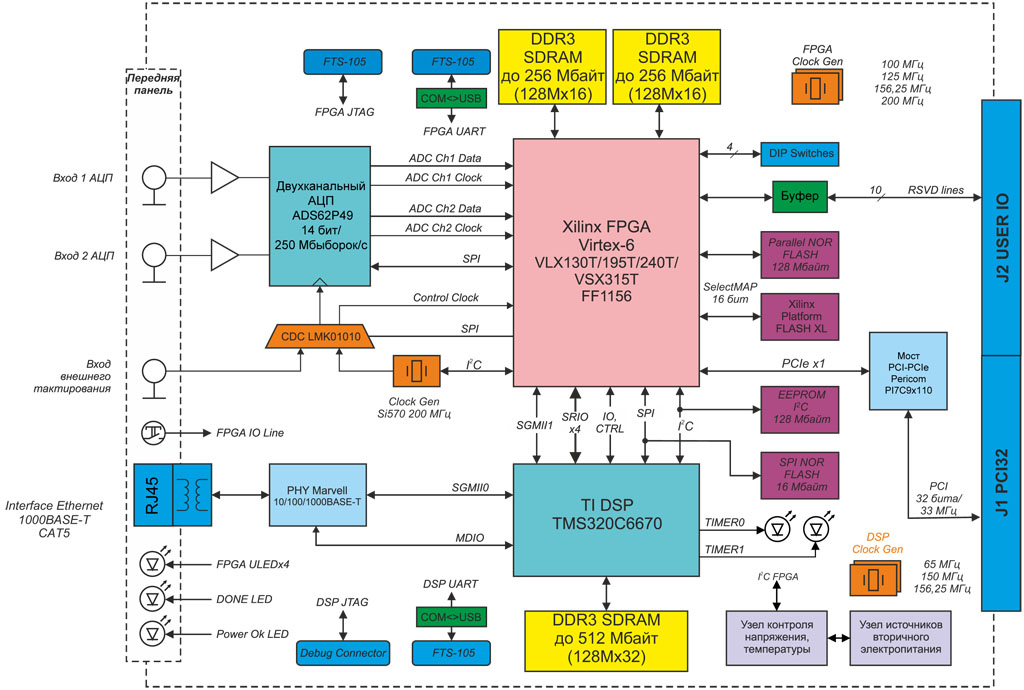

- Основная FPGA Xilinx

Virtex-6 семейства VLX или VSX в корпусе FF1156 - DSP TMS320C6670 компании Texas Instruments (TI) серии C667x

- Два канала АЦП: 14 бит 250 МГц

- Банк синхронного динамического RAM DDR3 SDRAM на DSP, объёмом 512 Мбайт

- Два независимых банка синхронного динамического RAM DDR3 SDRAM на SDRAM, объёмом 128 Мбайт (256 Мбайт) каждый

- Модуль

форм-фактора CompactPCI 3U шириной 4HP c системным интерфейсомPCI 32 бита/33 МГц , соответствующий стандарту PICMG 2.0 Rev 3.0

Описание

Особенности

Модуль XDSP-50

На модуле реализованы два канала аналого-цифрового преобразования с независимыми

аналоговыми трактами и общим тактированием. В качестве аналого-цифрового

преобразователя использована сдвоенная микросхема

Высокая производительность

Модуль XDSP-50 разработан для приложений, требующих высокую производительность,

высокую скорость передачи данных и низкую латентность. Модуль использует максимум

возможностей FPGA Xilinx

Области применения

Модуль-ускоритель обработки данных XDSP-50 предназначен для выполнения

двухканального аналого-цифрового преобразования видео- и радиосигналов с частотой

дискретизации до 250 МГц с их последующей цифровой обработкой на базе FPGA

Xilinx серии