Основные характеристики

- Высокопроизводительная FPGA Xilinx серий Kintex UltraScale

XCKU095/115, Virtex UltraScale XCVU080/095/125/160/190, Virtex UltraScale+

XCVU5P/7P/9P/13P объёмом свыше 3,7 млн. логических ячеек и числом умножителей

свыше 5,5 тыс.

- Два 64-х разрядных банка памяти DDR4-2133 SDRAM

общим объёмом до 16 Гбайт

- Установка субмодуля FMC+ в соответствии со стандартом

ANSI/VITA 57.4-2016 с поддержкой HSPC интерфейса,

включая 24 дуплексных линий MGT до 16,3 Гбит/с в каждой

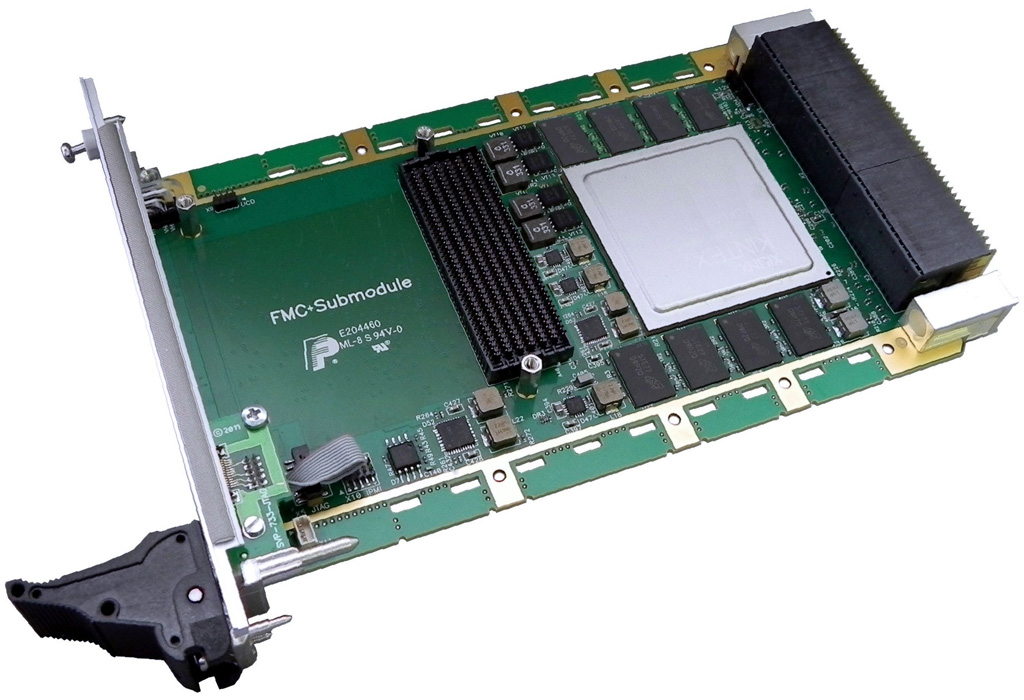

- Модуль форм-фактора VPX 3U, соответствующий стандартам:

ANSI/VITA 46.0-2013 (воздушное охлаждение),

ANSI/VITA 46.3-2012,

ANSI/VITA 46.4-2012,

ANSI/VITA 46.6-2013,

ANSI/VITA 57.4-2016

и ANSI/VITA 65-2010 (R2012)

- Поддержка системных интерфейсов: 2 × PCIe 1.0/2.0/3.0 x4

(DP01, 02), 2 × Gigabit Ethernet 1000BASE-BX (UTP01, 02)

- Возможность реализации до 4-х интерфейсов SRIO/Xilinx Aurora x4

через разъём P1 VPX (DP01–04), тип интерфейса определяется проектом FPGA

- Поддержка модуля тыльного ввода/вывода через разъём P2 VPX:

4 × дуплексных линий MGT, 20 × линий LVDS,

20 × линий КМОП 2,5 В

- Исполнения с воздушным и кондуктивным охлаждением

Описание

Особенности

Модуль SVP-737 форм-фактора VPX 3U предоставляет пользователю широкие

возможности цифровой обработки сигналов (ЦОС) на базе микросхемы программируемой

логики Kintex/Virtex UltraScale/UltraScale+ фирмы Xilinx, значительный объём встроенной

высокоскоростной памяти DDR4-2133 и широкий набор коммуникационных интерфейсов,

включая системные PCIe/SRIO/Xilinx Aurora, тыльного расширения

SRIO/Xilinx Aurora, а также ввода/вывода данных с субмодуля стандарта

ANSI/VITA 57.4-2016 FPGA Mezzanine Card Plus (FMC+).

Высокая производительность

Модуль SVP-737 предназначен для приложений, требующих предельно высокой

производительности цифровой обработки данных в реальном времени: фильтрации, спектральных

преобразований, корреляционной обработки и т. д. Пиковая производительность обработки

FPGA модуля на целочисленных операциях умножить-аккумулировать достигает

7300 млрд./с (XCVU13P: 12280 умножителей 27 × 18 бит, аккумулятор 48 бит,

600 МГц), а суммарная производительность обмена с памятью DDR4-2133 превышает

33 Гбайт/с (два 64-х-разрядных банка до 8 Гбайт каждый).

Наряду с высокой производительностью модуль предоставляет широкие возможности в части

организации системных интерфейсов через каналы DP01–04 VPX: поддерживаются

до 2-х каналов PCIe 1.0/2.0/3.0 x4 до 8 Гбит/c в линии/до 4-х каналов

SRIO 2.0 x4 до 6,25 Гбит/с, Xilinx Aurora 64b/66b до 10 Гбит/c,

2 канала Gigabit Ethernet. Тип системного интерфейса определяется проектом FPGA, причем

PCIe реализован с использованием встроенных аппаратных ядер FPGA, а SRIO,

Xilinx Aurora, Gigabit Ethernet — программных IP-Core, а также типом

объединительной платы и системного коммутатора. Реализована поддержка обмена данными с модулем

тыльного ввода/вывода через разъём P2 VPX посредством 4-х дуплексных пар MGT

до 10 Гбит/с в каждой и 20-и двунаправленных пар стандарта LVDS

до 1 Гбит/с в каждой.

Области применения

Модуль поддерживает установку субмодуля нового стандарта ANSI/VITA 57.4-2016

FPGA Mezzanine Card Plus (FMC+) с расширенными коммуникационными возможностями

в части последовательного мультигигабитного обмена, так, теперь поддерживается до 24-х

дуплексных пар MGT с пропускной способностью до 16,3 Гбит/с в каждой, реализован

дополнительный набор сигналов тактирования и синхронизации, что дает возможность построения

многоканальных систем приёма/передачи и обработки сигналов с использованием новейших

широкополосных АЦП/ЦАП со стандартом цифровых данных JESD204B.